CliffHangerNotes

From DaphneWiki

Contents |

ZPU

Battery circuit

When BRESET' is low (less than 0.6V, ie reset button is pressed), this puts Q3 into 'cut-off' mode, meaning the transistor will act as an open switch and therefore, the NVRAM (6E)'s VCC will be 5V and its CE' will also be 5V (disabled).

When RESET' is high (more than 0.6V, ie reset button is not being pressed), this put Q3 into 'saturation' mode, meaning the transistor will act as if its collector and emitter are short circuited. This will allow the output from the OR gate (2F, pin 6) to completely control the NVRAM's CE'. Due to the 2.2k resistor, R42, the NVRAM's VCC will not go below 4.5V even if 2F's pin 6 is low, because of the voltage coming from CR2.

GSI

TMS 9128 NL info

Pin-Out

| Pin | Name | Description |

| 1 | RAS' | [output] RAS' DRAM strobe |

| 2 | CAS' | [output] CAS' DRAM strobe |

| 3-10 | AD7-AD0 | [output] DRAM address output, AD0 is most significant |

| 11 | R/W' | [output] DRAM read/write' output |

| 12 | VSS | Ground |

| 13 | MODE | [input] VDP register mode |

| 14 | CSW' | [input] chip select write strobe |

| 15 | CSR' | [input] chip select read strobe |

| 16 | INT' | [output] chip generated interrupt at the start of new vblank |

| 17-24 | CD7-CD0 | [input/output] 8-bit data bus to whatever is controlling the VDP (usually the CPU). CD0 is the most significant bit. |

| 25-32 | RD7-RD0 | [input/output] DRAM data bus, RD0 is most significant |

| 33 | VDD | power supply, 5V |

| 34 | RST'/SYNC | [input] reset when low (under 0.6V), can be used to indicate 'sync active' when voltage is 10-12 (or above 9V). It appears that cliff hanger does use this to sync to the laserdisc video. Reset and sync are inactive when voltage is between 3.5-6 V. This is also referred to as a "sync input for EXTVDP". |

| 35 | B-Y | [output] analog color channel output |

| 36 | Y | [output] analog color channel output, may also include composite sync |

| 37 | CPUCLK | [output] not used |

| 38 | R-Y | [output] analog color channel output |

| 39 | XTAL2 | [input] clock input, 10.738635 MHz |

| 40 | XTAL1 | [input] clock input, 10.738635 MHz |

Csync and vsync separation

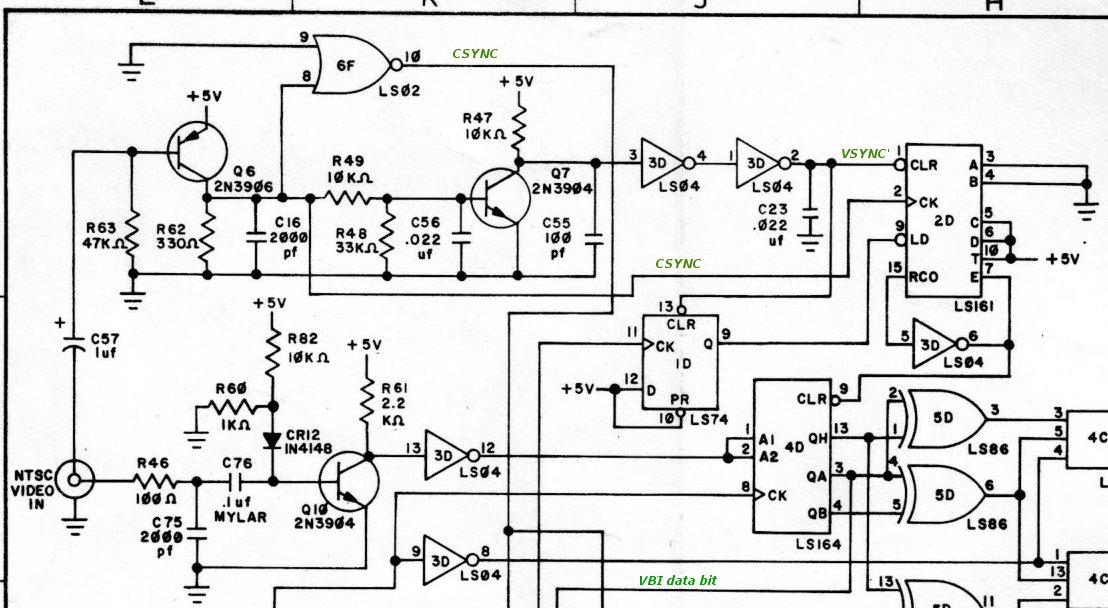

Cliff Hanger's GSI board separates both csync and vsync from an incoming NTSC signal.

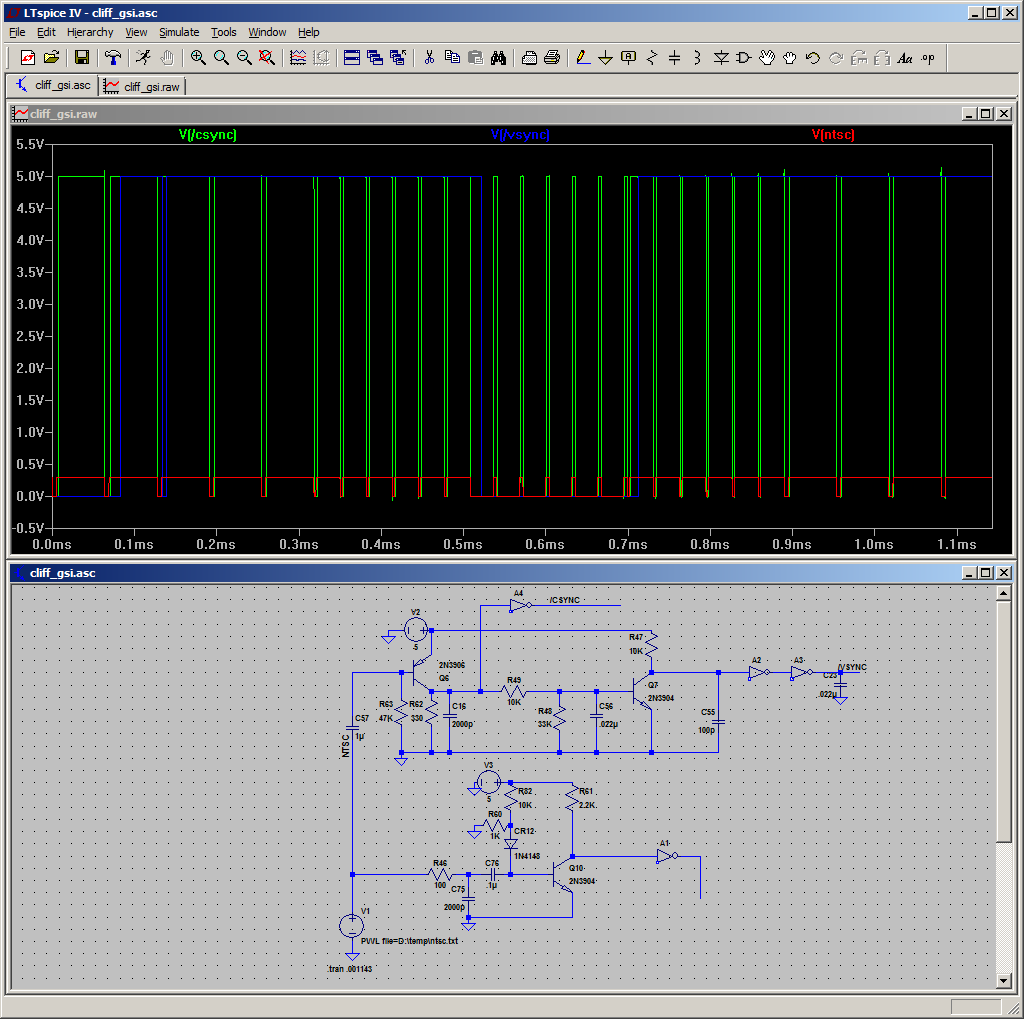

Here is the circuit simulated in LTSpice with a few lines coming before the beginning of the next top field:

Note that the vsync signal takes a little while to get 'primed' before being stable.

Manchester / picture number decoding

Not figured out yet.

UIB PCB characteristics

(Measured by Matt with a real PCB)

- Dimensions : 3.5" x 5"

- Mounting holes are 0.2" in diameter

- center of mounting holes horizontally are 2.9" apart from each other

- center of mounting holes vertically are 4.4" apart from each other

- all holes are 0.3" from PCB edges

Diode type appears to be 1N4148