BegasBattleNotes

From DaphneWiki

(→UART (17F / MC68B50P)) |

(→-5V) |

||

| (39 intermediate revisions not shown) | |||

| Line 1: | Line 1: | ||

= Main CPU = | = Main CPU = | ||

| + | |||

| + | == RD' and WR' == | ||

| + | |||

| + | RD' = R/W' NAND PHI2 | ||

| + | WR' = R'/W NAND PHI2 | ||

| + | |||

| + | See https://wilsonminesco.com/6502primer/ClkGen.html | ||

== Address decoding == | == Address decoding == | ||

| Line 114: | Line 121: | ||

= Power supply = | = Power supply = | ||

== -5V == | == -5V == | ||

| - | After inspecting the schematics and the PCB itself, the -5V rail appears to only be used by 9J (SN75188N) to be the low signal for the serial port. Therefore, it probably doesn't need much current. | + | After inspecting the schematics and the PCB itself, the -5V rail appears to only be used by 9J (SN75188N) to be the low signal for the serial port. Therefore, it probably doesn't need much current. |

| + | |||

| + | I substituted the -5V power input with -12V and left the game running for over an hour without any problems. | ||

== 16V == | == 16V == | ||

| Line 121: | Line 130: | ||

The audio amplifiers are MB3730 and have a max VCC voltage of 18V. It is designed to be powered by anything between 8V and 16V. So perhaps the audio amps could be powered by 12V instead of 16V and still work. | The audio amplifiers are MB3730 and have a max VCC voltage of 18V. It is designed to be powered by anything between 8V and 16V. So perhaps the audio amps could be powered by 12V instead of 16V and still work. | ||

| + | |||

| + | = RGB output = | ||

| + | |||

| + | == RA2 == | ||

| + | |||

| + | {| border="1" cellpadding="2" cellspacing="0" | ||

| + | |'''Pin''' | ||

| + | |'''In/Out''' | ||

| + | |'''Notes''' | ||

| + | |- | ||

| + | |1 | ||

| + | |I | ||

| + | |Power (5V) | ||

| + | |- | ||

| + | |2 | ||

| + | |O | ||

| + | |Red, 1 kOhm to pin 1 | ||

| + | |- | ||

| + | |3 | ||

| + | |I | ||

| + | |4.5 kOhm to pin 2 | ||

| + | |- | ||

| + | |4 | ||

| + | |I | ||

| + | |3.0 kOhm to pin 2 | ||

| + | |- | ||

| + | |5 | ||

| + | |I | ||

| + | |1.5 kOhm to pin 2 | ||

| + | |- | ||

| + | |6 | ||

| + | |O | ||

| + | |Green, 1 kOhm to pin 1 | ||

| + | |- | ||

| + | |7 | ||

| + | |I | ||

| + | |4.5 k Ohm to pin 6 | ||

| + | |- | ||

| + | |8 | ||

| + | |I | ||

| + | |3.0 kOhm to pin 6 | ||

| + | |- | ||

| + | |9 | ||

| + | |I | ||

| + | |1.5 kOhm to pin 6 | ||

| + | |- | ||

| + | |10 | ||

| + | |O | ||

| + | |Blue, 1 kOhm to pin 1 | ||

| + | |- | ||

| + | |11 | ||

| + | |I | ||

| + | |3.0 kOhm to pin 10 | ||

| + | |- | ||

| + | |12 | ||

| + | |I | ||

| + | |1.5 kOhm to pin 11 | ||

| + | |} | ||

| + | |||

| + | According to an LTSpice simulation I created, red and green will have an output range of 2.25V-5V and blue will have an output range of 2.5V-5V. | ||

| + | |||

| + | == RA3 == | ||

| + | |||

| + | NOTE: Pin 1 is tied to ground. Pins 2, 4, 6, and 8 are inputs. Pins 3 (Red), 5 (Green), 7 (Blue), and 9 (Csync) are outputs. | ||

| + | |||

| + | {| border="1" cellpadding="2" cellspacing="0" | ||

| + | |'''Pin to pin''' | ||

| + | |'''Resistance''' | ||

| + | |- | ||

| + | |1-3, 1-5, 1-7, 1-9 | ||

| + | |610 Ohm | ||

| + | |- | ||

| + | |2-3, 4-5, 6-7, 8-9 | ||

| + | |169 Ohm | ||

| + | |} | ||

| + | |||

| + | = Chromalux board = | ||

| + | |||

| + | Main IC is AN511: https://pdf1.alldatasheet.com/datasheet-pdf/view/113730/ETC1/AN5311.html | ||

= Sync signals = | = Sync signals = | ||

| Line 127: | Line 215: | ||

Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). The chip itself is labeled as "SONY 773A 3A" with "001" at the bottom. You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs). | Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). The chip itself is labeled as "SONY 773A 3A" with "001" at the bottom. You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs). | ||

| - | This custom IC takes in a 14. | + | Warren Ondras found a Sony manual that includes some info about this chip: http://www.rulecity.com/browse/laserdisc_game_stuff/begas/SEG2000AP_SM_SONY_EN_text.pdf |

| + | You can search for "773A" to find the relevant spots. (Pages 157, 158 are some of them) | ||

| + | |||

| + | This custom IC takes in a 14.31818 MHZ clock and five of its output are used: Composite SYNC, SGBLK, HSYNC2, VSYNC2, and SC. Exact clock frequency is 315/22 (see https://en.wikipedia.org/wiki/Crystal_oscillator_frequencies ) | ||

{| border="1" cellpadding="2" cellspacing="0" | {| border="1" cellpadding="2" cellspacing="0" | ||

| Line 133: | Line 224: | ||

|'''Description''' | |'''Description''' | ||

|'''Notes''' | |'''Notes''' | ||

| + | |- | ||

| + | |1 | ||

| + | |VR_IN / V_RESET | ||

| + | |Vertical reset? Possible way to sync to an external source. | ||

| + | |- | ||

| + | |2 | ||

| + | |CF OUT / Color frame pulse | ||

| + | |field indicator for PAL color? PAL/SECAM: low for 2.5 lines on even fields NTSC: same timing as L ALT | ||

| + | |- | ||

| + | |3 | ||

| + | |BF/CBLK OUT | ||

| + | |Blanking output (used to suppress active video? PAL/SECAM only?) | ||

|- | |- | ||

|4 | |4 | ||

|Composite Sync | |Composite Sync | ||

|Active low. Typical NTSC composite sync. Nothing unusual observed. | |Active low. Typical NTSC composite sync. Nothing unusual observed. | ||

| + | |- | ||

| + | |5 | ||

| + | |O/E OUT | ||

| + | |Field indicator; H=Odd, L=Even | ||

|- | |- | ||

|6 | |6 | ||

|SG BLK | |SG BLK | ||

| - | |Active low. May refer to "signal block" meaning when to prevent computer generated video from going to the monitor. | + | |Active low. May refer to "signal block" meaning when to prevent computer generated video from going to the monitor. low during HSYNC and front/back porch; also stays low for 25 lines on VSYNC |

| + | |- | ||

| + | |7 | ||

| + | |LALT OUT / L ALT | ||

| + | |Alternating line indicator output; low on odd lines, high on even lines | ||

|- | |- | ||

|8 | |8 | ||

|HSYNC 2 | |HSYNC 2 | ||

| - | |Active low. | + | |Active low. |

| + | |- | ||

| + | |9 | ||

| + | |4fsc OUT | ||

| + | |4x subcarrier clock output; only used for PAL/SECAM | ||

| + | |- | ||

| + | |10 | ||

| + | |4fsc IN | ||

| + | |4x subcarrier clock input; only used for PAL/SECAM | ||

|- | |- | ||

|11 | |11 | ||

|VSYNC 2 | |VSYNC 2 | ||

| - | |Active low. | + | |Active low. |

| + | |- | ||

| + | |12 | ||

| + | |GND | ||

| + | | | ||

| + | |- | ||

| + | |13 | ||

| + | |L ALTR IN / L ALT RESET | ||

| + | |high = reset alternating line indicator | ||

| + | |- | ||

| + | |14 | ||

| + | |TEST IN | ||

| + | |high = test mode (when _INT/EXT is also high); internal pulldown | ||

|- | |- | ||

|15 | |15 | ||

|SC | |SC | ||

|Stands for Sub-Carrier. Matches the color burst frequency. Runs at 3.58 MHz. | |Stands for Sub-Carrier. Matches the color burst frequency. Runs at 3.58 MHz. | ||

| + | |- | ||

| + | |16 | ||

| + | |EXT IN / _INT/EXT | ||

| + | |high = use external 4fsc clock? internal pulldown? PAL only? | ||

| + | |- | ||

| + | |17 | ||

| + | |MODE1 IN | ||

| + | |Mode select bit 1; low for NTSC (internal pulldown?) | ||

| + | |- | ||

| + | |18 | ||

| + | |MODE2 IN | ||

| + | |Mode select bit 2; low for NTSC (internal pulldown?) | ||

| + | |- | ||

| + | |19 | ||

| + | |HR IN / H RESET | ||

| + | |Horizontal reset input; should go low for 6.286 uS when HSYNC goes high | ||

| + | |- | ||

| + | |20 | ||

| + | |HCOM OUT / HCOMP | ||

| + | |Horizontal phase comparator output; only used for PAL/SECAM? | ||

| + | |- | ||

| + | |21 | ||

| + | |X1 | ||

| + | |Clock output. Connects to original crystal. Not really labeled. | ||

| + | |- | ||

| + | |22 | ||

| + | |X2 | ||

| + | |Clock input. Connects to original crystal. Not really labeled. | ||

| + | |- | ||

| + | |23 | ||

| + | |Fh OUT | ||

| + | |Something to do with horizontal phase; PAL only | ||

| + | |- | ||

| + | |24 | ||

| + | |5V | ||

| + | |Power | ||

|} | |} | ||

| + | |||

| + | === Exact cycle count to derive each signal === | ||

| + | Using the 14.318181 MHz clock (period of 22/315 uS), each output of the CX773A follows a fixed pattern. | ||

| + | |||

| + | The pattern is explained relative to '''Vsync2''' of '''top field''' being defined as cycle count 0 (arbitrary). | ||

| + | |||

| + | ''NOTE: it appears that Vsync2 and Hsync2 activate a little before a new line actually starts (Csync defines when the line actually starts). Perhaps the '2' designator refers to this quirk. However, for math convenience we will say that Vsync2 is the start of a field and Hsync2 is the start of a line.'' | ||

| + | |||

| + | ==== Vsync2 ==== | ||

| + | |||

| + | Activates (goes low) at cycle count 0. Deactivates (goes high) at 8190. Loops every 238875 cycles. 238875 * (22/315) = 16683.33 uS which is correct. (1001*1000/60) | ||

| + | |||

| + | ==== Hsync2 ==== | ||

| + | |||

| + | Activates (goes low) at cycle count 0. Deactivates (goes high) at 96. Loops every 910 cycles. 910 * (22/315) = 63.5555 uS which is correct. | ||

| + | |||

| + | ==== Csync ==== | ||

| + | |||

| + | Normally activates (goes low) 22 cycles after Hsync2 activates. Pulses lasts for 68 cycles, which means it deactivates 6 cycles before Hsync2. | ||

| + | |||

| + | However, the vertical sync area has special rules that are slightly different for top/bottom fields. | ||

| + | |||

| + | [[File:Cx773a_topField1.png|600px]] | ||

| + | |||

| + | [[File:Cx773a_topField2.png|600px]] | ||

| + | |||

| + | [[File:Cx773a_topField3.png|600px]] | ||

| + | |||

| + | [[File:Cx773a_bottomField0.png|600px]] | ||

| + | |||

| + | [[File:Cx773a_bottomField1.png|600px]] | ||

| + | |||

| + | {| border="1" cellpadding="2" cellspacing="0" | ||

| + | |'''Time interval name''' | ||

| + | |'''Time interval cycles''' | ||

| + | |'''Notes''' | ||

| + | |- | ||

| + | |t1 | ||

| + | |22 | ||

| + | |Space between HSync2 going low and CSync going low | ||

| + | |- | ||

| + | |t2 | ||

| + | |32 | ||

| + | |Thin pulse for lines 1-3 and 7-9 | ||

| + | |- | ||

| + | |t3 | ||

| + | |423 | ||

| + | |Rest of cycles representing a half line (455 cycles) | ||

| + | |- | ||

| + | |t4 | ||

| + | |387 | ||

| + | |The length of half of a horizontal line (455 cycles) minus the pulse | ||

| + | |- | ||

| + | |t5 | ||

| + | |68 | ||

| + | |Pulse duration for normal horizontal line | ||

| + | |- | ||

| + | |t6 | ||

| + | |878 | ||

| + | |Length of full horizontal line (910 cycles) minus thin pulse | ||

| + | |} | ||

| + | |||

| + | ==== SgBlk ==== | ||

| + | |||

| + | Normally, activates (goes low) with Hsync2. Stays active for 154 cycles. Loops every 910 cycles. | ||

| + | |||

| + | However, this signal also activates with Vsync2. Stays active for 18354 cycles when this happens (a little more than 20 lines). | ||

| + | |||

| + | So this signal is sort of a bitwise-AND of Hsync2 and Vsync2 with longer pulse durations. | ||

== NTSC composite signal notes == | == NTSC composite signal notes == | ||

| - | Color burst is 3.58 MHz and should last for 9 cycles. Wave shape is sine wave. Its range should be +/- 20 IRE which, if the video signal is 1Vp-p, means going from -142.857 mV to 142.857 mV . To verify, divide 20*1000/140 according to this page: https://en.wikipedia.org/wiki/IRE_(unit) | + | Color burst is 3.58 (315/88) MHz and should last for 9 cycles. Wave shape is sine wave. Its range should be +/- 20 IRE which, if the video signal is 1Vp-p, means going from -142.857 mV to 142.857 mV . To verify, divide 20*1000/140 according to this page: https://en.wikipedia.org/wiki/IRE_(unit) |

IRE for an NTSC signal can be derived by measuring voltage depth of HSYNC (or VSYNC) pulse. Said depth will be 40 IRE. The full range of the composite signal is 140 IRE. | IRE for an NTSC signal can be derived by measuring voltage depth of HSYNC (or VSYNC) pulse. Said depth will be 40 IRE. The full range of the composite signal is 140 IRE. | ||

| Line 173: | Line 409: | ||

https://electronics.stackexchange.com/questions/24979/changing-a-signals-dc-offset | https://electronics.stackexchange.com/questions/24979/changing-a-signals-dc-offset | ||

| + | |||

https://electronics.stackexchange.com/questions/163253/sine-wave-to-square-wave-schmitt-trigger | https://electronics.stackexchange.com/questions/163253/sine-wave-to-square-wave-schmitt-trigger | ||

| + | |||

| + | https://electronics.stackexchange.com/questions/467186/sine-to-square-wave-converted-using-only-transistors | ||

Spartan 3E docs that include info about clocks: https://www.xilinx.com/support/documentation/user_guides/ug331.pdf | Spartan 3E docs that include info about clocks: https://www.xilinx.com/support/documentation/user_guides/ug331.pdf | ||

| Line 234: | Line 473: | ||

Lock Pulse from player: According to LDP-1000A manual, this is used to superimpose graphics over the player's image. The chroma board apparently makes use of it. | Lock Pulse from player: According to LDP-1000A manual, this is used to superimpose graphics over the player's image. The chroma board apparently makes use of it. | ||

| + | |||

| + | LDP-2000 service manual has a lock pulse jack which may be similar and which may have the following characteristics: | ||

| + | |||

| + | TTL, active high (see page 150/313, SY-30 of LDP-2000 service manual for how I came to this conclusion). | ||

| + | The inverse of "JUMP FIELD OUT" signal. | ||

| + | |||

| + | |||

| + | Size of plug is 2.5mm diameter and 14.66mm length (according to Mike Treu). So pretty non-standard. | ||

| + | |||

| + | [[File:LockPulse.jpg|300px]] | ||

== BNC output voltage levels == | == BNC output voltage levels == | ||

| Line 269: | Line 518: | ||

|A3 | |A3 | ||

|TxD | |TxD | ||

| - | |Outgoing, +12V to -5V | + | |Outgoing, +12V to -5V |

|- | |- | ||

|A4 | |A4 | ||

| - | |CTS | + | |CTS |

|Tied to A5. | |Tied to A5. | ||

|- | |- | ||

|A5 | |A5 | ||

| - | |RTS | + | |RTS |

|Tied to A4 | |Tied to A4 | ||

|- | |- | ||

|A6 | |A6 | ||

| - | |DTR | + | |DTR |

|12V through 1k resistor | |12V through 1k resistor | ||

|- | |- | ||

|A7 | |A7 | ||

| - | |Signal ground | + | |Signal ground |

|GND | |GND | ||

|- | |- | ||

|A8 | |A8 | ||

| | | | ||

| - | |Not connected | + | |Not connected |

|- | |- | ||

|} | |} | ||

| Line 373: | Line 622: | ||

=== Software configuration === | === Software configuration === | ||

| - | Control set with 0x03 (E104) | + | Control set with 0x03 (E104). Master reset of MC68B50. |

| - | Control set with 0x96 (E109) | + | Control set with 0x96 (E109). Bit 7 - enable RX interrupt. Bits 6:5 - RTS' = low, transmit interrupt disabled. Bits 4:2 - 8 bits, 1 stop bit. Bits 1:0 - divide incoming clock by 64. |

| + | |||

| + | === Transmission speed === | ||

| + | |||

| + | Surprisingly, the game communicates with the laserdisc player at 1200 bps. | ||

| + | |||

| + | You can confirm this yourself by taking the incoming clock ( 9.804 MHz ), dividing it by 128 ( 76.59 kHz ) and then dividing that again by 64 (a configuration setting on the MC68B50) to get 1.1967 kHz (about 1200 bps). | ||

| + | |||

| + | = Mounting hole = | ||

| + | |||

| + | The mounting hole on the PCB is 0.75" up from 16K pin 24 and 0.3" to the right (if board is held so that pin 1 is to the top and left). | ||

| + | |||

| + | The hole itself is 0.1" in diameter. | ||

| + | |||

| + | The nylon stand-off is a little less than 0.4" in 'diameter' at its widest point. | ||

Latest revision as of 21:36, 31 October 2023

Contents |

Main CPU

RD' and WR'

RD' = R/W' NAND PHI2 WR' = R'/W NAND PHI2

See https://wilsonminesco.com/6502primer/ClkGen.html

Address decoding

Two PALs are used to aid with address decoding (instead of the usual '138's). Changes in PAL outputs occur when the CPU's PHI2 goes low.

PAL (10H)

| Pin(s) | In/Out? | Description |

| 1-3 | In | A15-A13 |

| 4-7 | In | A3-A0 |

| 8 | In | CPU PHI2 |

| 9 | In | CPU R/W' |

| 11 | In | Memory Disable (not sure what the intent is for this) |

| 12 | Out | R'/W (read/write flipped?). Unconfirmed. |

| 13 | Out | Goes low when A0-A3 has the value of 3. Used by the other PAL as an input. |

| 14-19 | Out | ROM enable lines (active low) |

Memory map

| Address Range | Description |

| 0x0000-0x07FF | RAM #1 (unconfirmed) |

| 0x0800-0xFFF | RAM #2 (unconfirmed) |

| 0x1000 R | |

| 0x1000 W | Lower nibble appears to be used to disable laserdisc video (unconfirmed). See video PCB schematic page 14/14, around 7C. Lowest 2 bits appear to control the coin blockers (unconfirmed). |

| 0x1001 R | |

| 0x1001 W | NMI Ack' |

| 0x1002 R | |

| 0x1003 R | Read from video PCB. Bit 7 = VBLANK. Bit 6 = BLK2. It doesn't look like any other bits can be read here. |

| 0x1004 W | AM2950. Sound CPU I/O? |

| 0x1005 R | |

| 0x1006 R | MC68B50 Serial port control |

| 0x1006 W | MC68B50 Serial port control |

| 0x1007 R | MC68B50 Serial port data rx |

| 0x1007 W | MC68B50 Serial port data tx |

| 0x4000-0x5FFF | ROM5 |

| 0x6000-0x7FFF | ROM4 |

| 0x8000-0x9FFF | ROM3 |

| 0xA000-0xBFFF | ROM2 |

| 0xC000-0xDFFF | ROM1 |

| 0xE000-0xFFFF | ROM0 |

Power supply

-5V

After inspecting the schematics and the PCB itself, the -5V rail appears to only be used by 9J (SN75188N) to be the low signal for the serial port. Therefore, it probably doesn't need much current.

I substituted the -5V power input with -12V and left the game running for over an hour without any problems.

16V

The 16V rail appears to be used only by the audio amplifier. I did a visual inspection of the PCB to confirm this.

The audio amplifiers are MB3730 and have a max VCC voltage of 18V. It is designed to be powered by anything between 8V and 16V. So perhaps the audio amps could be powered by 12V instead of 16V and still work.

RGB output

RA2

| Pin | In/Out | Notes |

| 1 | I | Power (5V) |

| 2 | O | Red, 1 kOhm to pin 1 |

| 3 | I | 4.5 kOhm to pin 2 |

| 4 | I | 3.0 kOhm to pin 2 |

| 5 | I | 1.5 kOhm to pin 2 |

| 6 | O | Green, 1 kOhm to pin 1 |

| 7 | I | 4.5 k Ohm to pin 6 |

| 8 | I | 3.0 kOhm to pin 6 |

| 9 | I | 1.5 kOhm to pin 6 |

| 10 | O | Blue, 1 kOhm to pin 1 |

| 11 | I | 3.0 kOhm to pin 10 |

| 12 | I | 1.5 kOhm to pin 11 |

According to an LTSpice simulation I created, red and green will have an output range of 2.25V-5V and blue will have an output range of 2.5V-5V.

RA3

NOTE: Pin 1 is tied to ground. Pins 2, 4, 6, and 8 are inputs. Pins 3 (Red), 5 (Green), 7 (Blue), and 9 (Csync) are outputs.

| Pin to pin | Resistance |

| 1-3, 1-5, 1-7, 1-9 | 610 Ohm |

| 2-3, 4-5, 6-7, 8-9 | 169 Ohm |

Chromalux board

Main IC is AN511: https://pdf1.alldatasheet.com/datasheet-pdf/view/113730/ETC1/AN5311.html

Sync signals

Sync Generation

Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). The chip itself is labeled as "SONY 773A 3A" with "001" at the bottom. You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs).

Warren Ondras found a Sony manual that includes some info about this chip: http://www.rulecity.com/browse/laserdisc_game_stuff/begas/SEG2000AP_SM_SONY_EN_text.pdf You can search for "773A" to find the relevant spots. (Pages 157, 158 are some of them)

This custom IC takes in a 14.31818 MHZ clock and five of its output are used: Composite SYNC, SGBLK, HSYNC2, VSYNC2, and SC. Exact clock frequency is 315/22 (see https://en.wikipedia.org/wiki/Crystal_oscillator_frequencies )

| Pin | Description | Notes |

| 1 | VR_IN / V_RESET | Vertical reset? Possible way to sync to an external source. |

| 2 | CF OUT / Color frame pulse | field indicator for PAL color? PAL/SECAM: low for 2.5 lines on even fields NTSC: same timing as L ALT |

| 3 | BF/CBLK OUT | Blanking output (used to suppress active video? PAL/SECAM only?) |

| 4 | Composite Sync | Active low. Typical NTSC composite sync. Nothing unusual observed. |

| 5 | O/E OUT | Field indicator; H=Odd, L=Even |

| 6 | SG BLK | Active low. May refer to "signal block" meaning when to prevent computer generated video from going to the monitor. low during HSYNC and front/back porch; also stays low for 25 lines on VSYNC |

| 7 | LALT OUT / L ALT | Alternating line indicator output; low on odd lines, high on even lines |

| 8 | HSYNC 2 | Active low. |

| 9 | 4fsc OUT | 4x subcarrier clock output; only used for PAL/SECAM |

| 10 | 4fsc IN | 4x subcarrier clock input; only used for PAL/SECAM |

| 11 | VSYNC 2 | Active low. |

| 12 | GND | |

| 13 | L ALTR IN / L ALT RESET | high = reset alternating line indicator |

| 14 | TEST IN | high = test mode (when _INT/EXT is also high); internal pulldown |

| 15 | SC | Stands for Sub-Carrier. Matches the color burst frequency. Runs at 3.58 MHz. |

| 16 | EXT IN / _INT/EXT | high = use external 4fsc clock? internal pulldown? PAL only? |

| 17 | MODE1 IN | Mode select bit 1; low for NTSC (internal pulldown?) |

| 18 | MODE2 IN | Mode select bit 2; low for NTSC (internal pulldown?) |

| 19 | HR IN / H RESET | Horizontal reset input; should go low for 6.286 uS when HSYNC goes high |

| 20 | HCOM OUT / HCOMP | Horizontal phase comparator output; only used for PAL/SECAM? |

| 21 | X1 | Clock output. Connects to original crystal. Not really labeled. |

| 22 | X2 | Clock input. Connects to original crystal. Not really labeled. |

| 23 | Fh OUT | Something to do with horizontal phase; PAL only |

| 24 | 5V | Power |

Exact cycle count to derive each signal

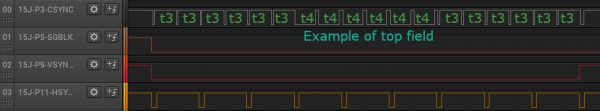

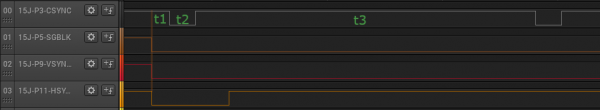

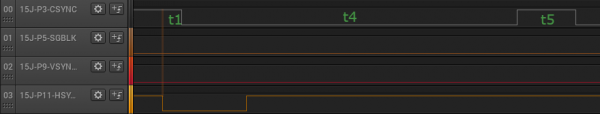

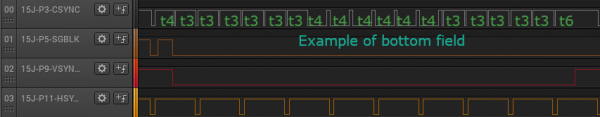

Using the 14.318181 MHz clock (period of 22/315 uS), each output of the CX773A follows a fixed pattern.

The pattern is explained relative to Vsync2 of top field being defined as cycle count 0 (arbitrary).

NOTE: it appears that Vsync2 and Hsync2 activate a little before a new line actually starts (Csync defines when the line actually starts). Perhaps the '2' designator refers to this quirk. However, for math convenience we will say that Vsync2 is the start of a field and Hsync2 is the start of a line.

Vsync2

Activates (goes low) at cycle count 0. Deactivates (goes high) at 8190. Loops every 238875 cycles. 238875 * (22/315) = 16683.33 uS which is correct. (1001*1000/60)

Hsync2

Activates (goes low) at cycle count 0. Deactivates (goes high) at 96. Loops every 910 cycles. 910 * (22/315) = 63.5555 uS which is correct.

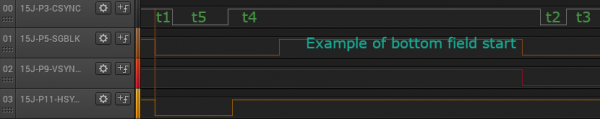

Csync

Normally activates (goes low) 22 cycles after Hsync2 activates. Pulses lasts for 68 cycles, which means it deactivates 6 cycles before Hsync2.

However, the vertical sync area has special rules that are slightly different for top/bottom fields.

| Time interval name | Time interval cycles | Notes |

| t1 | 22 | Space between HSync2 going low and CSync going low |

| t2 | 32 | Thin pulse for lines 1-3 and 7-9 |

| t3 | 423 | Rest of cycles representing a half line (455 cycles) |

| t4 | 387 | The length of half of a horizontal line (455 cycles) minus the pulse |

| t5 | 68 | Pulse duration for normal horizontal line |

| t6 | 878 | Length of full horizontal line (910 cycles) minus thin pulse |

SgBlk

Normally, activates (goes low) with Hsync2. Stays active for 154 cycles. Loops every 910 cycles.

However, this signal also activates with Vsync2. Stays active for 18354 cycles when this happens (a little more than 20 lines).

So this signal is sort of a bitwise-AND of Hsync2 and Vsync2 with longer pulse durations.

NTSC composite signal notes

Color burst is 3.58 (315/88) MHz and should last for 9 cycles. Wave shape is sine wave. Its range should be +/- 20 IRE which, if the video signal is 1Vp-p, means going from -142.857 mV to 142.857 mV . To verify, divide 20*1000/140 according to this page: https://en.wikipedia.org/wiki/IRE_(unit)

IRE for an NTSC signal can be derived by measuring voltage depth of HSYNC (or VSYNC) pulse. Said depth will be 40 IRE. The full range of the composite signal is 140 IRE.

Genlock / PLL stuff for color burst

https://electronics.stackexchange.com/questions/14361/synchronising-to-a-colour-burst

( MC1378P and MC44144 mentioned, both out of production)

Page about color burst PLL: https://books.google.com/books?id=_spKr2qoRKwC&pg=PA313#v=onepage&q&f=false

Techniques for converting analog sine wave into square wave:

https://electronics.stackexchange.com/questions/24979/changing-a-signals-dc-offset

https://electronics.stackexchange.com/questions/163253/sine-wave-to-square-wave-schmitt-trigger

Spartan 3E docs that include info about clocks: https://www.xilinx.com/support/documentation/user_guides/ug331.pdf

Chroma Board

Signals from VDO-1 (bottom) PCB that are sent to Chroma board

| CN2 Pin from VDO-1 (bottom) PCB | CN1 Pin on Chroma PCB | Description |

| B3 | 2 | 12V |

| A5 | 3 | 5V |

| B5 | 3 | 5V |

| A7 | 9 | Analog red |

| B7 | 4 | DSP Sel (I assume this means whether to display laserdisc video or computer generated video) |

| A8 | 8 | Analog green |

| B8 | 5 | SUB PC BLKING aka BL (related to SG BLK) |

| A9 | 7 | Analog blue |

| B9 | 6 | csync |

| A10 | 1 | Ground |

| B10 | 10 | Ground |

Other stuff the chroma board may use

Lock Pulse from player: According to LDP-1000A manual, this is used to superimpose graphics over the player's image. The chroma board apparently makes use of it.

LDP-2000 service manual has a lock pulse jack which may be similar and which may have the following characteristics:

TTL, active high (see page 150/313, SY-30 of LDP-2000 service manual for how I came to this conclusion). The inverse of "JUMP FIELD OUT" signal.

Size of plug is 2.5mm diameter and 14.66mm length (according to Mike Treu). So pretty non-standard.

BNC output voltage levels

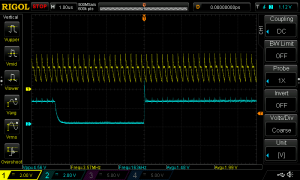

Sub carrier

Yellow is Sub-Carrier (color burst).

Input specs say signal may be 2V(p-p) +/- 0.5V(p-p) 75 ohm

Composite sync

Blue is composite sync. Blue averages about 2.4V high.

Input specs say signal may be 4V(p-p) +/- 1V(p-p) 75 ohm

Serial I/O

VDO-2 CN2

| CN2 Pin from VDO-2 (top) PCB | Name | Notes |

| A1 | GND | |

| A2 | RxD | Incoming |

| A3 | TxD | Outgoing, +12V to -5V |

| A4 | CTS | Tied to A5. |

| A5 | RTS | Tied to A4 |

| A6 | DTR | 12V through 1k resistor |

| A7 | Signal ground | GND |

| A8 | Not connected |

UART (17F / MC68B50P)

| Pin | Name | Notes |

| 1 | GND | |

| 2 | Rx Data | |

| 3 | Rx Clock | Tied to 16D-12 |

| 4 | Tx clock | Tied to 16D-12 |

| 5 | RTS' | Not connected |

| 6 | Tx Data | To 9J-2 |

| 7 | IRQ' | To main CPU IRQ (I think?) |

| 8 | CS0 | To 5V |

| 9 | CS2' | To 14E-9 |

| 10 | CS1 | To 5V? (schematic hard to read) |

| 11 | RS | Tied to an address bus line |

| 12 | VCC | To 5V |

| 13 | R/W' | To CPU R/W' it appears |

| 14 | E (Enable) | to something related to main CPU |

| 15-22 | D7-D0 | Data bus |

| 23 | DCD' | Tied to GND |

| 24 | CTS' | Tied to GND |

Logic Analyzer Notes

Data bus holds a valid writable value when CS2' is low and E is high.

Software configuration

Control set with 0x03 (E104). Master reset of MC68B50. Control set with 0x96 (E109). Bit 7 - enable RX interrupt. Bits 6:5 - RTS' = low, transmit interrupt disabled. Bits 4:2 - 8 bits, 1 stop bit. Bits 1:0 - divide incoming clock by 64.

Transmission speed

Surprisingly, the game communicates with the laserdisc player at 1200 bps.

You can confirm this yourself by taking the incoming clock ( 9.804 MHz ), dividing it by 128 ( 76.59 kHz ) and then dividing that again by 64 (a configuration setting on the MC68B50) to get 1.1967 kHz (about 1200 bps).

Mounting hole

The mounting hole on the PCB is 0.75" up from 16K pin 24 and 0.3" to the right (if board is held so that pin 1 is to the top and left).

The hole itself is 0.1" in diameter.

The nylon stand-off is a little less than 0.4" in 'diameter' at its widest point.