BegasBattleNotes

From DaphneWiki

(→Sync Generation) |

|||

| Line 6: | Line 6: | ||

== Sync Generation == | == Sync Generation == | ||

| - | Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs). | + | Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). The chip itself is labeled as "SONY 773A 3A" with "001" at the bottom. You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs). |

This custom IC takes in a 14.3182 MHZ clock and five of its output are used. Exact clock frequency is 315/22 (see https://en.wikipedia.org/wiki/Crystal_oscillator_frequencies ) | This custom IC takes in a 14.3182 MHZ clock and five of its output are used. Exact clock frequency is 315/22 (see https://en.wikipedia.org/wiki/Crystal_oscillator_frequencies ) | ||

Revision as of 18:27, 2 December 2021

Contents |

Power supply

-5V

After inspecting the schematics and the PCB itself, the -5V rail appears to only be used by 9J (SN75188N) to be the low signal for the serial port. Therefore, it probably doesn't need much current and could potentially be substituted with -12V with no ill effects.

Sync signals

Sync Generation

Video sync signals are generated by what appears to be a custom Sony chip called the CX 773A (I couldn't find any info about this by googling for it). The chip itself is labeled as "SONY 773A 3A" with "001" at the bottom. You can find it on the Bega's Battle schematic called "DSP Control Decode" and it is at position 16K on the VDO-1 (bottom) PCB (the one with the two BNC outputs).

This custom IC takes in a 14.3182 MHZ clock and five of its output are used. Exact clock frequency is 315/22 (see https://en.wikipedia.org/wiki/Crystal_oscillator_frequencies )

| Pin | Description | Notes |

| 4 | Composite Sync | Active low. Typical NTSC composite sync. Nothing unusual observed. |

| 6 | SG BLK | Active low. May refer to "signal block" meaning when to prevent computer generated video from going to the monitor. For top field, starts at beginning of line 1 and ends when line 21 begins, and otherwise goes low when HSync goes low (and lasts a little bit longer than HSync pulses). |

| 8 | HSYNC 2 | Active low. Appears to run at a constant 15.73 kHz frequency with no variation. Each line is 63.56 uS long. Each pulse lasts for 6.72 uS. Usually starts a little before csync and ends a little after. Goes low at the same time as SG BLK. |

| 11 | VSYNC 2 | Active low. For top field, starts at the beginning of line 1 and ends at the end of line 9. No apparent delay relative to csync. Each pulse lasts for 0.5721 ms and the frequency is a constant 59.93 Hz, with a period of 16.69 ms. |

| 15 | SC | Stands for Sub-Carrier. Matches the color burst frequency. Runs at 3.58 MHz. |

NTSC composite signal notes

Color burst is 3.58 MHz and should last for 9 cycles. Wave shape is sine wave. Its range should be +/- 20 IRE which, if the video signal is 1Vp-p, means going from -142.857 mV to 142.857 mV . To verify, divide 20*1000/140 according to this page: https://en.wikipedia.org/wiki/IRE_(unit)

IRE for an NTSC signal can be derived by measuring voltage depth of HSYNC (or VSYNC) pulse. Said depth will be 40 IRE. The full range of the composite signal is 140 IRE.

Genlock / PLL stuff for color burst

https://electronics.stackexchange.com/questions/14361/synchronising-to-a-colour-burst

( MC1378P and MC44144 mentioned, both out of production)

Page about color burst PLL: https://books.google.com/books?id=_spKr2qoRKwC&pg=PA313#v=onepage&q&f=false

Techniques for converting analog sine wave into square wave:

https://electronics.stackexchange.com/questions/24979/changing-a-signals-dc-offset https://electronics.stackexchange.com/questions/163253/sine-wave-to-square-wave-schmitt-trigger

Spartan 3E docs that include info about clocks: https://www.xilinx.com/support/documentation/user_guides/ug331.pdf

Chroma Board

Signals from VDO-1 (bottom) PCB that are sent to Chroma board

| CN2 Pin from VDO-1 (bottom) PCB | CN1 Pin on Chroma PCB | Description |

| B3 | 2 | 12V |

| A5 | 3 | 5V |

| B5 | 3 | 5V |

| A7 | 9 | Analog red |

| B7 | 4 | DSP Sel (I assume this means whether to display laserdisc video or computer generated video) |

| A8 | 8 | Analog green |

| B8 | 5 | SUB PC BLKING aka BL (related to SG BLK) |

| A9 | 7 | Analog blue |

| B9 | 6 | csync |

| A10 | 1 | Ground |

| B10 | 10 | Ground |

Other stuff the chroma board may use

Lock Pulse from player: According to LDP-1000A manual, this is used to superimpose graphics over the player's image. The chroma board apparently makes use of it.

BNC output voltage levels

Sub carrier

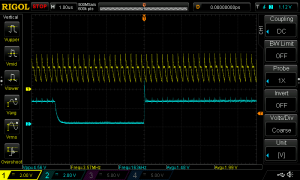

Yellow is Sub-Carrier (color burst).

Input specs say signal may be 2V(p-p) +/- 0.5V(p-p) 75 ohm

Composite sync

Blue is composite sync. Blue averages about 2.4V high.

Input specs say signal may be 4V(p-p) +/- 1V(p-p) 75 ohm

Serial I/O

VDO-2 CN2

| CN2 Pin from VDO-2 (top) PCB | Name | Notes |

| A1 | GND | |

| A2 | RxD | Incoming |

| A3 | TxD | Outgoing, +12V to -5V (apparently) |

| A4 | CTS ? | Tied to A5. |

| A5 | RTS ? | Tied to A4 |

| A6 | DTR ? | 12V through 1k resistor |

| A7 | Signal ground? | GND |

| A8 | Not connected? |

UART (17F / MC68B50P)

| Pin | Name | Notes |

| 1 | GND | |

| 2 | Rx Data | |

| 3 | Rx Clock | Tied to 16D-12 |

| 4 | Tx clock | Tied to 16D-12 |

| 5 | RTS' | Not connected |

| 6 | Tx Data | To 9J-2 |

| 7 | IRQ' | To main CPU IRQ (I think?) |

| 8 | CS0 | To 5V |

| 9 | CS2' | To 14E-9 |

| 10 | CS1 | To 5V? (schematic hard to read) |

| 11 | RS | Tied to an address bus line |

| 12 | VCC | To 5V |

| 13 | R/W' | To CPU R/W' it appears |

| 14 | E (Enable) | to something related to main CPU |

| 15-22 | D7-D0 | Data bus |

| 23 | DCD' | Tied to GND |

| 24 | CTS' | Tied to GND |